Вып. 3(50)

#### ИНФОРМАТИКА ИНФОРМАЦИОННЫЕ СИСТЕМЫ

УДК 51:33(075.8)

# Алгоритм выбора оптимального набора конфигурируемых строго самосинхронных логических элементов

К. М. Иванова<sup>1</sup>, А. Ю. Скорнякова<sup>1,2</sup>

<sup>1</sup>Пермский национальный исследовательский политехнический университет Россия, 614990, г. Пермь, ул. Комсомольский пр., 29

<sup>2</sup> ПАО "Пермская научно-производственная приборостроительная компания" Россия, 614990, г. Пермь, ул. 25 Октября, 106 ivanovaksenijamikh@yandex.ru; +7-922-362-78-60 juris-plot@mail.ru; +7-951-949-65-22

Описывается разработанный алгоритм выбора оптимального набора новых конфигурируемых строго самосинхронных (ССС) логических элементов, в котором учитываются комплексные характеристики, такие как: количество транзисторов, площадь, быстродействие и потребляемая мощность. В качестве вариантов в составе конфигурируемого логического блока программируемых логических интегральных схем (ПЛИС) рассматриваются следующие предложенные универсальные логические элементы: ССС-генератор функций на основе стандартных логических элементов базового матричного кристалла – БМК (ГФ), ССС-генератор функций на основе универсального логического элемента программируемых логических интегральных схем – ПЛИС (LUT-ST), ССС-генератор систем функций на основе дешифрации водного набора DC LUT-ST и ССС-эквивалент программируемой логической матрицы – ПЛМ (ДНФ-LUT-ST).

Ключевые слова: строго самосинхронные схемы; БМК; ПЛИС; сложность.

DOI: 10.17072/1993-0550-2020-3-85-90

#### Введение

По мере приближения проектных норм изготовления микросхем к единицам нанометра, т. е., практически к размерам молекул, где начинают проявляться квантовые эффекты, становятся все более очевидными серьезные проблемы глобальной синхронизации. В качестве альтернативы может быть использована самосинхронизация, как вариант асинхронного подхода, предложенного Д. Маллером еще в конце 50-х годов ХХ в. [1]. Этот подход, имея определенные существенные недостатки, как бы находился в "резерве" до

начала эры наноэлектроники. Однако существует обоснованное мнение, что иного варианта для "квантоники" просто может не существовать. В то же время, существующие на данный момент в РФ методы реализации ССС автоматов, ориентированы в основном, на "жесткую" логику БМК. Распространено утверждение о невозможности совмещения ССС-подхода и программируемой логики. Исследования показали, что создание универсального ССС-элемента, т. е. конфигурируемого, настраиваемого на реализацию заданной логической функции, в СДНФ и в ДНФ возможно.

<sup>©</sup> Иванова К. М., Скорнякова А. Ю., 2020

Разработанные методы прошли экспериментальную проверку с использованием систем схемотехнического моделирования "Ковчег" и NI Multisim (проверка функционирования для размерностей входных переменных 1,2,3). Кроме этого выполнено успешное топологическое моделирование в системе MircoWind. Наконец, подтверждено свойство полумодулярности помощью САПР c "Forcage" подсистема "Tranal", разработанной в Институте проблем информатики Российской академии наук Федерального исследовательского центра "Информатика и управление" Российской академии наук исследовательской группой Ю.А. Степченкова [3-6], с которой кафедра "Автоматика и телемеханика" ПНИПУ поддерживает многолетние партнерские связи.

#### Новые конфигурируемые СССлогические элементы

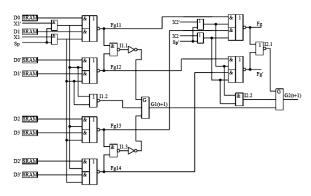

С целью реализации конфигурируемого ССС-логического элемента в БМК предлагается использование элементов 2И-2ИЛИ-НЕ [1, 7] (рис. 1), формирующих мультиплексор, входы данных которого настраиваются или с помощью констант 0,1 или путем использования ячеек конфигурационной оперативной памяти SRAM.

При этом вводится двойственный канал, индикаторы окончания переходного процесса и элементы Маллера (Г-триггеры).

Рис. 1. Элемент ССС-ГФ двух переменных

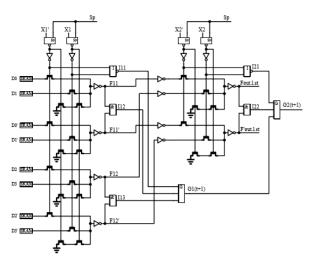

Предлагаемый ССС-генератор функций на основе универсального логического элемента программируемых логических интегральных схем — ПЛИС (LUT-ST) [8, 9] изображен на рис. 2.

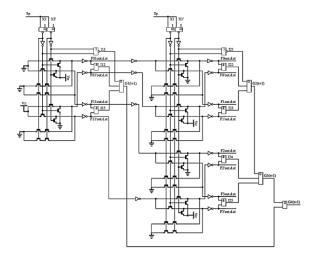

ССС-генератор систем функций на основе дешифрации водного набора DC LUT-ST [10] изображен на рис. 3.

ССС-эквивалент программируемой логической матрицы — ПЛМ, реализующий конфигурируемые конъюнкции для системы функций в ДНФ (ДНФ-LUT-ST) [11] изображен на рис. 4.

Моделирование подтвердило строгую самосинхронность (полумодулярность) предложенных элементов.

Для оценки сложности в числе транзисторов в зависимости от числа переменных n получены соответствующие формулы. Оценены показатели задержки, площади кристалла, мощности потребления для n=1,2,3.

С целью оценки показателей для больших значений n выполнена аппроксимация, учитывающая экспоненциальный рост сложности устройства.

Рис. 2. Элемент 2-LUT-ST с Г-триггером и индикатором входов

Рис. 3. Элемент 2-DC LUT-ST с двойственным каналом, индикатором и G-триггером

Рис. 4. Элемент – конфигурируемая конъюнкция ДНФ LUT-ST двух разрядов

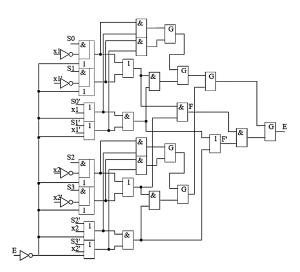

### Алгоритм оптимизации набора ССС конфигурируемых логических элементов

Для выбора оптимального набора из нескольких заданных логических элементов задается абстрактное множество:

$$M = \left\{ m_i \right\}_{i=\overline{1},i},\tag{1}$$

где  $m_i$  — выбранные генераторы функций  $(\Gamma \Phi)$ , l — количество  $\Gamma \Phi$ .

По множеству M находится булеан B:

$$B(M) = \{b | b \subseteq M\} \setminus \{\emptyset\}. \tag{2}$$

После чего необходимо найти множество E — множество всевозможных наборов ЛЭ, т. е. для каждого элемента  $b \in B$  определяются  $E_i \subset E, \ i = \overline{1,|E|}$  — множества наборов ЛЭ, такие что:

$$E_{i} = \left\{ \bigcup_{j=1}^{|b|} a_{j} * f_{j} \middle| \sum_{t=1}^{|M|} a_{t} = N, f_{t} \in M, t = \overline{1, |M|} \right\}, (3)$$

где N — количество допустимых ЛЭ,  $i = \overline{1,|E|}$  .

Далее необходимо вычислить таблицу сложности T размера,  $|E| \times |C|$ , где C — множество столбцов, для каждого элемента  $c_i \in C$  задаются параметры:

$$(n_i, m_i, y_i, m_{dnf}, k)_{i=\overline{1,|C|}},$$

где  $n_i$  — количество переменных,  $m_i$  — количество функций,  $y_i$  — количество систем,  $m_{dnf}$  — параметр для ДНФ-LUT-ST, k — количество конъюнкций. Каждой строке таблицы T соответствует набор ЛЭ  $e_i \in E$ ,  $i=\overline{1,|E|}$ .

Элементы в строке заполняются согласно следующему алгоритму:

1. Для соответствующего набора ЛЭ  $e_i \in E$  находим минимальный поднабор ЛЭ  $e_1' \subset e_i, \ i=\overline{1,|E|},$  такой что:

$$e'_1 = \min \sum_{j=1}^{|e'_1|} a_j \cdot f_j(n_1, m_1, y_1, m_{dnf}, k),$$

где  $a_j$  – количество ЛЭ соответствующей ЛФ –  $f_i$  ,  $j=\overline{1,|e_i'|}$  .

2. Последующие элементы в строке находятся, как и в п.1, но вместо набора ЛЭ  $e_i \in E$  берется набор  $e_i \cap e'_1 \cap ... \cap e'_{j-1}$ ,  $i = \overline{1,|E|}, \ j = \overline{1,|C|}$ , т.е. набор, который получен как пересечение исходного набора ЛЭ с минимальными поднаборами, полученными в предыдущих столбцах.

Вычисление элементов в строке выполняется до тех пор, пока в исходном наборе  $e_i \in E$ ,  $i=\overline{1,|E|}$  достаточно ЛЭ. Если, при вычислении следующего элемента, в строке недостаточно ЛЭ, то расчет прекращается и алгоритм переходит к следующему набору ЛЭ.

После того, как таблица сложности T полностью вычислена, происходит поиск множества оптимальных наборов ЛЭ по каждой характеристике. Для количества транзисторов, площади и потребляемой мощности находятся минимальные покрытия, т.е. покрытия из минимальных элементов, а для быстродействия — покрытие, в котором содержится минимальный элемент из максимальных значений ЛФ каждой строки табл. T.

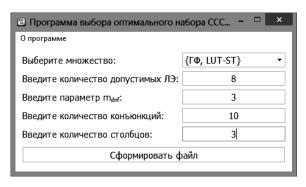

Для более удобного использования данного алгоритма была разработана программа на языке C++ – "Программа выбора оптимального набора ССС ЛЭ" (рис. 5).

Рис. 5. Главное окно программы — "Программа выбора оптимального набора ССС ЛЭ"

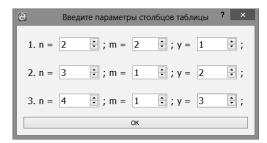

После того, как пользователь введет необходимые значения и нажмет на кнопку "Сформировать файл", откроется окно ввода параметров (рис. 6) для каждого столбца таблины сложности T.

Рис. 6. Окно ввода параметров столбцов таблицы сложности, где n — количество переменных, m — количество функций, y — количество систем

При нажатии на кнопку "ОК", сформируется файл, в формате \*.xlsx, с вычисленными значениями таблицы сложности и оптимальными наборами ЛЭ. А также отобразится диалоговое окно с графическим представлением найденных значений в плоскости (S, T, P) (рис. 7).

#### Примеры выбора оптимальных наборов элементов

Рассмотрим применение алгоритма с использованием разработанной программы.

**Пример 1.** Задано множество из двух ССС-генераторов функций:  $\Gamma\Phi$  и LUT-ST. Количество допустимых ЛЭ равно 8. Параметры для столбцов задаются строками (2, 2, 1), (3, 1, 2) и (4, 1, 3). Необходимо найти оптимальный набор ЛЭ.

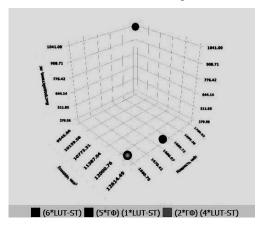

Решение. При помощи программы, разработанной с использованием алгоритма, описанного выше, получили оптимальные наборы:

- 1. (6\*LUT-ST),

- 2.  $(5*\Gamma\Phi)(1*LUT-ST)$ ,

- 3.  $(2*\Gamma\Phi)$  (4\*LUT-ST).

Количественные характеристики, для полученных оптимальных наборов ЛЭ, определены табл. 1. Цветом выделены минимальные значения для каждого параметра.

Таблица 1. Значения количественных характеристик для наборов ЛЭ: 1-(6\*LUT-ST),  $2-(5*\Gamma\Phi)(1*LUT-ST)$ ,  $3-(2*\Gamma\Phi)(4*LUT-ST)$

| № | L, шт | S, mkm <sup>2</sup> | Т, пс  | P, мк $B$ т |

|---|-------|---------------------|--------|-------------|

| 1 | 2744  | 12614,5             | 379,56 | 1683,92     |

| 2 | 2858  | 9545,86             | 1041   | 1709,03     |

| 3 | 2744  | 12329,8             | 379,56 | 1660,76     |

Графический результат программы вычисленных данных представлен на рис. 7 и рис. 8.

Рис. 7. Графическое представление таблицы сложности из примера 1, с выделением множества оптимальных наборов ЛЭ

Рис. 8. Графическое представление множества оптимальных наборов  $\Pi$ 3 из примера I

Количество транзисторов не является показательной характеристикой, поэтому полученное множество можно сократить до двух оптимальных наборов:  $(5*\Gamma\Phi)$  (1\*LUT-ST) и  $(2*\Gamma\Phi)$  (4\*LUT-ST).

ГФ и LUT-ST реализуют системы, которые зависят от количества заданных функций, т.е. при небольших заданных параметрах будут выигрывать наборы, состоящие из этих ЛФ. При реализации большего количества функций будут выигрывать наборы, состоящие из DC LUT-ST и ДНФ-LUT-ST.

#### Рассмотрим на примере.

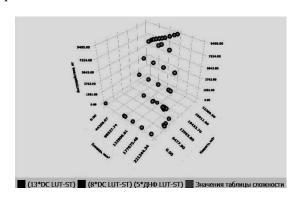

**Пример 2.** Задано множество из четырех ССС генераторов функций: ГФ, LUT-ST, DC LUT-ST и ДНФ-LUT-ST. Количество допустимых ЛЭ равно 16. Параметры для столбцов задаются строками (4, 3, 1), (5, 4, 2), (3, 3, 5), (4, 5, 1), (6, 3, 3), (1, 4, 1) и  $m_{dnf} = 8$ , k = 10.

Необходимо найти оптимальный набор ЛЭ.

Решение. Как результат работы программы, получили следующие оптимальные наборы ЛЭ:

- 1. (13\*DC LUT-ST),

- 2. (8\*DC LUT-ST) (5\*ДНФ LUT-ST).

Для каждого полученного набора ЛЭ, вычисленные значения характеристик представлены в табл. 2. Цветом выделены минимальные значения для каждого параметра.

Таблица 2. Значения количественных характеристик для наборов:  $1 - (13*DC\ LUT-ST)$  и  $2 - (8*DC\ LUT-ST)$  ( $5*ДНФ\ LUT-ST$ )

| No | L, шт | S, mkm <sup>2</sup> | Т, пс | P, мк $B$ т |

|----|-------|---------------------|-------|-------------|

| 1  | 26348 | 218903              | 3102  | 7301.69     |

| 2  | 69122 | 92034,8             | 9405  | 19519.4     |

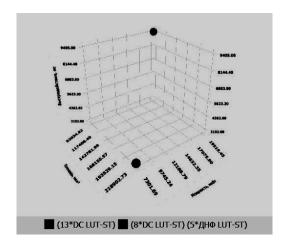

Графический результат программы вычисленных данных представлен на рис. 9 и рис. 10.

Рис. 9. Графическое представление таблицы сложности из примера 2, с выделением множества оптимальных наборов ЛЭ

Рис. 10. *Графическое представление множества оптимальных наборов ЛЭ из примера 2*

#### Выводы

Предлагаемый алгоритм и программа позволяют учитывать сразу несколько количественных характеристик для выбора оптимального набора логических элементов, таких как: количество транзисторов, площадь, быстродействие и потребляемая мощность. Причем, если требуется реализовать небольшое количество систем с минимальным количеством функций, то выигрышные наборы будут состоять из ГФ и LUT-ST, а для реализации более "крупных" систем будут определять наборы из DC LUT-ST и ДНФ-LUT-ST.

Дальнейшее развитие направления ССС ПЛИС возможно в области реализации последовательностной конфигурируемой логики и самосинхронной передачи информации в матрицах коммутации ПЛИС.

Кроме того, необходима модификация ранее предложенных алгоритмов диагностирования с учетом новых разработанных ССС логических элементов.

#### Список литературы

- 1. Скорнякова А.Ю., Тюрин С.Ф. Синтез самосинхронных генераторов логических функций. Вестник Пермского Национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2020. № 34. С. 168–185.

- 2. *Скорнякова А.Ю.* Оценка сложности самосинхронных логических элементов FPGA // Вестник Пермского университета. Серия: Математика. Механика. Информатика. 2019. № 4 (47). С. 86–89.

- 3. Библиотека элементов для проектирования самосинхронных полузаказных БМК микросхем серий 5503/5507 / Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. М.: Издво ИПИ РАН, 2014. 296 с.

- 4. Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю., Дьяченко Д.Ю. Устойчивость самосинхронных комбинационных схем к кратковременным логическим сбоям // Системы и средства информатики. 2020. Т. 30, № 2. С. 4–10.

- 5. Степченков Ю.А., Каменских А.Н., Тюрин С.Ф., Дьяченко Ю.Г. Отказоустойчивый самосинхронный последовательно-параллельный порт: варианты реализации // Си-

- стемы и средства информатики. 2016. Т. 26, № 3. С. 48–59.

- 6. Степченков Ю.А., Каменских А.Н., Тюрин С.Ф., Рождественский Ю.В. Модели отказоустойчивых самосинхронных схем // Системы и средства информатики. 2016. Т. 26, № 4. С. 19–30.

- 7. *Тюрин С.Ф., Скорнякова А.Ю.* Самосин-хронный универсальный логический элемент для реализации систем функций // Инженерный вестник Дона. 2017. № 1.

- 8. *Тюрин С.Ф., Скорнякова А.Ю.* Универсальный логический элемент для самосинхронной схемы // Вестник Рязанского

- государственного радиотехнического университета. 2017. № 61. С. 41–45.

- 9. Тюрин С.Ф., Каменских А.Н., Скорнякова А.Ю. (Плотникова А.Ю.) Программируемое логическое устройство: патент РФ №2601145; опубл. 27.10.2016, Бюл. № 30.

- Тюрин С.Ф., Скорнякова А.Ю. Программируемое логическое устройство: патент РФ № 2653301; опубл. 07.05.2018, Бюл. № 13.

- Тюрин С.Ф., Скорнякова А.Ю. Программируемое логическое устройство: патент РФ № 2653304; опубл. 07.05.2018, Бюл. № 13.

## Algorithm for choosing the optimal set of configurable self-timed logic gates

#### K. M. Ivanova<sup>1</sup>, A. Yu. Skornyakova<sup>1,2</sup>

<sup>1</sup>Perm National Research Polytechnic University; 29, Komsomolsky Av., Perm, 614990, Russia <sup>2</sup>JSC "Perm Scientific-Industrial Instrument Making Company"; 25<sup>th</sup> October st., 106, Perm, 614990, Russia ivanovaksenijamikh@yandex.ru; +7-922-362-78-60 juris-plot@mail.ru; +7-951-949-65-22

The article describes the developed algorithm for choosing the optimal set of new configurable strictly self-timed (SST) logic elements, which takes into account complex characteristics, such as: the number of transistors, area, time delay and power consumption. The following proposed universal logic elements are considered as options as part of a configurable logic block of programmable logic integrated circuits (FPGAs): SST function generator based on standard logic elements of the uncommitted logic array - ULA, SST function generator based on universal logic element of programmable logic integrated circuits - FPGA (LUT-ST), SST generator of function systems based on the decoding of the water set DC LUT-ST and SST equivalent of a programmable logic matrix - PLM (DNF-LUT-ST).

**Keywords:** self-timed circuits; ULA; PLD; complexity.