УДК 681.32

## Особенности формализации транзисторных схем логических элементов

## С. Ф. Тюрин

Пермский государственный национальный исследовательский университет Россия, 614990, г. Пермь, ул. Букирева, 15 tyurinsergfeo@yandex.ru; +7-952-32-02-510

КМОП-схемы (комплементарная структура металл-оксид-полупроводник; англ. CMOS, complementary metal-oxide-semiconductor) как правило — последовательно-параллельные и описываются дизьюнктивной нормальной формой (ДНФ) реализуемых ими логических функций. С целью упрощения схемы применяют скобочную форму. Эти структуры могут быть описаны соответствующей цепочкой символов (словом). Однако в ряде случаев используют схемы, которые не могут быть описаны цепочками. Кроме того, иногда в схему вводят так называемые мостики-транзисторы. В статье анализируются особенности логического описания таких схем и предпринимается попытка их формализации.

**Ключевые слова:** логическая функция; ДНФ; КМОП-схема; логический элемент; транзистор.

DOI: 10.17072/1993-0550-2018-3-129-133

### Введение

Реализация логики в виде КМОП-схемы [1] предполагает представление логической функции в виде двух подсхем — подсхемы подключения "+" источника питания и подсхемы подключения шины "ноль вольт" [2]. Эти два представления логической функции должны быть ортогональны, т. е. каждое представление является отрицанием другого. Например, самая простая функция — инверсия (отрицание) сигнала на входе х:

$$f(x) = \overline{x}.\tag{1}$$

Эта функция и является функцией подключения "+":

$$f(x)_{+} = \overline{x}. \tag{2}$$

А функция подключения шины "ноль вольт" является ее отрицанием:

$$f(x)_0 = x. (3)$$

Получаем условную КМОП-схему, где входная переменная х подается сразу на два транзистора (на верхний и на нижний), см. рис. 1.

Рис. 1. Условная схема КМОП-инвертора

Таким образом, если х=0, то активируется верхний транзистор р-проводимости х и ток течет от "+" (Vdd) на выход f(x). Если x=1, активируется нижний транзистор ппроводимости x и ток течет от выхода f(x) на шину "ноль вольт". Ситуация, когда не активна ни та, ни другая подсхема, недопустима это приводит к так называемому третьему состоянию (ни ноль, ни единица) или высокому импедансу на выходе. Кроме того, применяется только в элементах с тремя состояниями на выходе. Они используются как шинные формирователи в микропроцессорных системах. Другая проблемная ситуация, когда активны обе подсхемы, что приводит к КЗ – короткому замыканию.

<sup>©</sup> Тюрин С. Ф., 2018

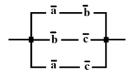

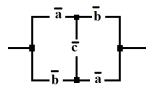

Еще более упрощенная схема реализации функции 2И-НЕ имеет вид (рис. 2):

Рис. 2. Условная схема элемента 2И-НЕ

Таким образом, реализуется логическая функция

$$f(ab)_{+} = \overline{ab} = \overline{a} \vee \overline{b}, \tag{4}$$

(параллельное соединение транзисторов  $\overline{a}$  и  $\overline{b}$ ) и ортогональная ей функция с последовательным соединением транзисторов a и b:

$$f(ab)_0 = \overline{ab} = ab. \tag{5}$$

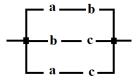

Очевидно, что в случае 2ИЛИ-НЕ все будет наоборот (см. рис. 3).

Рис. 3. Условная схема элемента 2ИЛИ-НЕ

$$f(ab) = \overline{a \vee b} = \overline{ab}.$$

(6)

Как строится последовательнопараллельная схема в случае, если в функции переменные без инверсии? Рассмотрим классический пример двоичного полного сумматора для двух бит a, b и входного переноса c.

### 1. Реализация двоичного сумматора

Сумматор реализует две функции, сумму:

$$s(abc) = \overline{abc} \vee \overline{abc} \vee \overline{abc} \vee abc, \qquad (7)$$

и перенос в следующий разряд

$$p(abc) = ab \lor bc \lor ac. \tag{8}$$

Начнем с переноса (8). Для упрощения будем пока рассматривать только верхнюю подсхему. Поскольку в функции (8) нет ни

одной переменной с инверсией, обычно реализуют инверсную функцию, а потом используют инвертор (1):

$$\overline{p}(abc) = \overline{ab \lor bc \lor ac} =

= (\overline{a} \lor \overline{b})(\overline{b} \lor \overline{c})(\overline{a} \lor \overline{c}) =

= (\overline{b} \lor \overline{ac})(\overline{a} \lor \overline{c}) = \overline{ab} \lor \overline{bc} \lor \overline{ac}.$$

(9)

Заметим, что такой результат (инверсия равна той же функции, но все переменные проинверсированы) объясняется самодвойственностью (8).

Таким образом, получаем:

Рис. 4. Условная схема реализации инверсии переноса

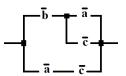

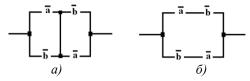

Реализация рис. 4 дает сложность 6. Легко видеть, что двойственная схема имеет вид

Рис. 5. Двойственная схема реализации инверсии переноса

Таким образом, реализация (рис. 4, 5) дает суммарную сложность 12 (транзисторов). Переход к скобочной форме позволяет сэкономить два транзистора:

$$\overline{p(abc)} = \overline{b(a \lor c)} \lor \overline{ac}.$$

(10)

Получаем реализацию:

Рис. 6. Условная схема реализации инверсии переноса по скобочной форме логической функции

Сложнее с функцией суммы. Если мы имеем так называемые парафазные входы [1], то есть помимо переменной X есть еще ее инверсия NX, то требуется 12 транзисторов в одной части КМОП подсхемы и 12 в другой, всего 24 (помимо 3 инверторов).

С учетом того, что для реализации переноса нужно 12 транзисторов (10 – схема рис. 6 и 2 – инвертор), получаем всего 36. И это на один разряд! А их в настоящее время нужно не менее 64.

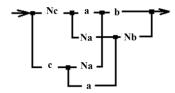

В работе [1] предложена вот такая подсхема:

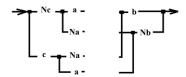

Рис. 7. Условная схема элемента реализации суммы в виде последовательно-параллельной структуры с "переплетением"

Такая реализация имеет сложность 8+8=16. Существенное снижение сложности! Обратим внимание на ортогональные участки схемы (a, Na), (b, Nb), (c, Nc). То есть, всегда активирован только один из альтернативных путей! Однако в этом случае скобочная форма не позволяет описать структуру схемы. Представим функцию s(a, Na, b, Nb, c, Nc) (7) в виде структуры с разрывом:

Рис. 8. Разрыв структуры с "переплетением"

Предложим описание схемы рис. 8 в виде двух деревьев с разрывом ... и корнями • по аналогии с [3, 4]:

$$\begin{array}{ccc}

& \stackrel{a \to 1}{Nc} & \\

& Nc & \\

& Na \to 2 & (1)b & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& &$$

Стрелки с номерами описывают соответствующие соединения. Проверим реализацию суммы. Действительно,

$$s(a, Na, b, Nb, c, Nc) = \\ = \overline{abc} \lor abc \lor a\overline{bc} \lor \overline{abc} = \\ = (Nc) ab \lor (Nc)(Na)(Nb) \lor c(Na)(b) \lor c a(Nb).$$

(12)

Функция суммы (12) тоже самодвойственна, поэтому структура второй подсхемы повторяет рис. 7.

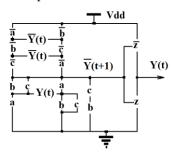

## 2. Универсальный элемент ПЛИС

Описанные выше схемы реализуют только одну заданную логическую функцию. Программируемые логические интегральные схемы (ПЛИС) типа FPGA (field-programmable gate array) содержат универсальные (настраиваемые на реализацию заданной функции [5], генераторы логических функций) логические элементы LUT (Look-Up Table), которые представляют собой деревья так называемых передающих МОП-транзисторов (это уже не комплементарные схемы, хотя в них используются, например, КМОП-инверторы). Так LUT на три переменных *а,b,c* можно представить в виде дерева:

$$d_{0} \rightarrow \overline{a} \rightarrow \overline{b}$$

$$d_{1} \rightarrow a \rightarrow \overline{c}$$

$$d_{2} \rightarrow \overline{a} \rightarrow \overline{c}$$

$$d_{3} \rightarrow a \rightarrow \overline{b}$$

$$d_{4} \rightarrow \overline{a} \rightarrow \overline{b}$$

$$d_{5} \rightarrow a \rightarrow \overline{b}$$

$$d_{6} \rightarrow \overline{a} \rightarrow \overline{c}$$

$$d_{7} \rightarrow a \rightarrow \overline{b}$$

$$d_{1} \rightarrow a \rightarrow \overline{c}$$

$$d_{2} \rightarrow a \rightarrow \overline{c}$$

$$d_{3} \rightarrow a \rightarrow \overline{c}$$

$$d_{4} \rightarrow a \rightarrow \overline{c}$$

$$d_{5} \rightarrow a \rightarrow \overline{c}$$

$$d_{7} \rightarrow a \rightarrow \overline{c}$$

$$d_{7} \rightarrow a \rightarrow \overline{c}$$

$$d_{1} \rightarrow a \rightarrow \overline{c}$$

$$d_{2} \rightarrow a \rightarrow \overline{c}$$

$$d_{3} \rightarrow a \rightarrow \overline{c}$$

$$d_{4} \rightarrow a \rightarrow \overline{c}$$

$$d_{5} \rightarrow a \rightarrow \overline{c}$$

$$d_{7} \rightarrow a \rightarrow \overline{c}$$

В выражении (13) в отличие от (11) номера стрелок не указаны в связи с интуитивно-ясной древовидной структурой элемента (схемы). Настройка на реализацию заданной функции в совершенной дизьюнктивной нормальной форме (СДНФ) осуществляется по входам данных d дерева. В отличие от КМОПсхем здесь нет второй подсхемы, но требование ортогональности трактуется так: в каждый момент времени должна быть активирована одна и только одна ветвь дерева.

#### 3. Мостиковые схемы

Еще одна КМОП-реализация мажоритарной функции-переноса (8) имеет так называемый мостик (рис. 9).

Рис. 9. Условная подсхема реализации инверсии переноса с мостиком

Мостиком называется элемент схемы (транзистор в данном случае), в котором ток может течь в разных направлениях при разных наборах переменных (в отличие от вышерассмотренных схем). Для описания такой структуры используем разложение Шеннона по мостиковому транзистору  $\overline{c}$  (рис. 10):

Рис. 10. Разложение Шеннона подсхемы реализации инверсии переноса с мостиком

$$c: a) \ c = 1 \ 6) \ c = 0.$$

Тем не менее, возможно также представление схемы рис. 9 в виде следующего выражения:

$$\overline{p(abc)} = \overline{ab} \vee \overline{bc} \vee \overline{ac} =

= \overline{ab} \vee \overline{ba} \vee \overline{aca} \vee \overline{bcb}.$$

(14)

Выражение (14) описывает все варианты протекания тока слева направо на рис. 9. Используем подход разложения Шеннона для анализа схемы рис. 11.

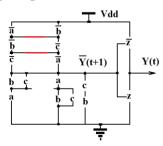

Рис. 11. Некоторая мостиковая схема

Получим две подсхемы: при Y(t)=0, в этом случае активны транзисторы в верхней части подсхемы – подключения "+" источника питания и возникает связь двух концов мостика. В нижней подсхеме в этом случае образуется разрыв (рис. 12).

Рис. 12. Некоторая мостиковая схема  $npu\ Y(t)=0$

Получаем:

$$\overline{Y}(t+1)_{+(Y=0)} = (\overline{a} \vee \overline{b})(\overline{b} \vee \overline{c})(\overline{c} \vee \overline{a}).$$

(15)

$$\overline{Y}(t+1)_{0(Y=0)} = (b \lor c)a \lor a(b \lor c) \lor cb.$$

(16)

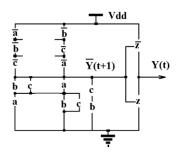

В случае Y(t)=0 все наоборот (рис. 13).

Рис. 13. Некоторая мостиковая схема  $npu\ Y(t)=1$

Получаем:

$$\overline{Y}(t+1)_{+(Y=0)} = \overline{abc} \vee \overline{bca}.$$

(17)

$$\overline{Y}(t+1)_{0(Y=0)} = (b \lor c \lor a)(a \lor b \lor c) \lor cb. \tag{18}$$

Дизъюнкция (15) и (17), (16) и (18) дает искомое описание мостиковой схемы.

#### Выводы

Таким образом, логика транзисторных КМОП-схем чаще всего последовательно-параллельная и формализуется ДНФ и скобочной формой логической функции, что позволяет уменьшить количество транзисторов. Последовательно-параллельная схема с переплетением не может быть непосредственно представлена цепочкой символов.

В статье предложена формализация таких схем с введением разрыва, что позволяет получить описание в виде двух поддеревьев. Формальное описание в виде одного дерева может быть использовано для универсальных элементов LUT ПЛИС. Мостиковые КМОПсхемы могут быть формализованы с использованием разложения Шеннона по символу мостика. В случае наличия нескольких мостиков по разным переменным необходимо рассматривать все возможные комбинации присвоения значений 0,1 этим переменным.

В дальнейшем целесообразно исследовать вопрос редукции последовательно — параллельных схем в мостиковые с учетом оценок сложности. То есть определить условия того, когда редуцированная схема будет проще исходной.

## Список литературы

- 1. Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гринфельд Ф.И., Филимоненко О.П., Морозов Н.В., Степченков Д.Ю. Библиотека элементов для проектирования самосинхронных полузаказных БМК микросхем серий 5503/5507 М.: ИПИ РАН, 2014. 296 с.

- 2. *Угрюмов Е.П.* Цифровая схемотехника: учеб. пособие. 2-е изд., перераб. и доп. СПб.: БХВ-Петербург, 2007. 782 с.

- 3. *Тюрин С.Ф., Каменских А.Н.* Методика комбинированного резервирования в самосинхронных схемах // Вестник Пермского уни-

- верситета. Серия: Математика. Механика. Информатика. 2016. № 4(35). С. 63–67.

- 4. Тюрин С.Ф., Каменских А.Н. Формальная система вывода резервированных КМДП структур отказоустойчивых самосинхронных схем // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2016. № 2(18). С. 120–135.

- 5. Строгонов А., Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри. URL: http://www.kite.ru/articles/plis/2010\_11\_56.php (дата обращения: 11.06.2017).

# Features of the transistors logic gates formalization

S. F. Tyurin

Perm State University; 15, Bukireva st., Perm, 614990, Russia

tyurinsergfeo@yandex.ru; +7 952-320-02-510

CMOS-circuits (complementary structure metal-oxide-semiconductor) are usually sequential-parallel and are described by the disjunctive normal form of the logical functions they realize. To simplify the scheme, a bracket form is used. An appropriate string of symbols can describe these structures. However, in a number of cases, schemes that can not be described by chains are used. In addition, sometimes the circuit introduces so-called bridge transistors. The article analyzes the features of the logical description of such schemes and attempts to formalize such schemes are made.

**Keywords:** Logic function; DNF; CMOS-circuit; gate; transistor.